digital

DPV11 serial synchronous interface user guide

digital equipment corporation ● merrimack, new hampshire

# Copyright © 1980 by Digital Equipment Corporation

#### All Rights Reserved

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

This document was set on DIGITAL's DECset-8000 computerized typesetting system.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DIGITAL | DECsystem-10 | MASSBUS |

|---------|--------------|---------|

| DEC     | DECSYSTEM-20 | OMNIBUS |

| PDP     | DIBOL        | OS/8    |

| DECUS   | EduSystem    | RSTS    |

| UNIBUS  | VAX          | RSX     |

| DECLAB  | VMS          | IAS     |

|         |              | MINC-11 |

# **CONTENTS**

|           |                                                         | Page |

|-----------|---------------------------------------------------------|------|

| CHAPTER 1 | INTRODUCTION                                            |      |

| 1.1       | SCOPE                                                   | 1-1  |

| 1.2       | DPV11 GENERAL DESCRIPTION                               | 1-1  |

| 1.3       | DPV11 OPERATION                                         | 1-2  |

| 1.4       | DPV11 FEATURES                                          |      |

| 1.5       | GENERAL SPECIFICATIONS                                  |      |

| 1.5.1     | Environmental Specifications                            | 1-2  |

| 1.5.2     | Electrical Specifications                               | 1-3  |

| 1.5.3     | Performance Parameters                                  | 1-3  |

| 1.6       | DPV11 CONFIGURATIONS                                    | 1-3  |

| 1.7       | EIA STANDARDS OVERVIEW                                  | 1-3  |

| CHAPTER 2 | INSTALLATION                                            |      |

| 2.1       | INTRODUCTION                                            | 2-1  |

| 2.2       | UNPACKING AND INSPECTION                                | 2-1  |

| 2.3       | PRE-INSTALLATION REQUIREMENTS                           | 2-1  |

| 2.4       | INSTALLATION                                            | 2-6  |

| 2.4.1     | Verification of Hardware Operation                      | 2-7  |

| 2.4.2     | Connection to External Equipment/Link Testing           | 2-8  |

| 2.5       | TEST CONNECTORS                                         | 2-8  |

| CHAPTER 3 | REGISTER DESCRIPTIONS AND PROGRAMMING INFORMATION       |      |

| 3.1       | INTRODUCTION                                            | 3-1  |

| 3.2       | DPV11 REGISTERS AND DEVICE ADDRESSES                    | 3-1  |

| 3.3       | REGISTER BIT ASSIGNMENTS                                |      |

| 3.3.1     | Receive Control and Status Register (RXCSR)             |      |

| 3.3.2     | Receive Data and Status Register (RDSR)                 | 3-2  |

| 3.3.3     | Parameter Control Sync/Address Register (PCSAR)         | 3-2  |

| 3.3.4     | Parameter Control and Character Length Register (PCSCR) |      |

| 3.3.5     | Transmit Data and Status Register (TDSR)                |      |

| 3.4       | DATA TRANSFERS                                          |      |

| 3.4.1     | Receive Data                                            |      |

| 3.4.2     | Transmit Data                                           |      |

| 3.5       | INTERRUPT VECTORS                                       | 3-21 |

|           |                                                         |      |

# CONTENTS (Cont)

| ·           |                                             | Page        |

|-------------|---------------------------------------------|-------------|

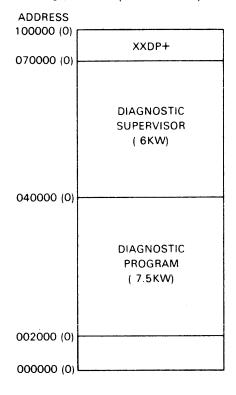

| APPENDIX A  | DIAGNOSTIC SUPERVISOR SUMMARY               |             |

| <b>A</b> .1 | INTRODUCTION                                | A-1         |

| A.2         | VERSIONS OF THE DIAGNOSTIC SUPERVISOR       |             |

| A.3         | LOADING AND RUNNING A SUPERVISOR DIAGNOSTIC |             |

| A.4         | SUPERVISOR COMMANDS                         |             |

| A.4.1       | Command Switches                            |             |

| A.4.2       | Control/Escape Characters Supported         | A-4         |

| A.5         | THE SETUP UTILITY                           | <b>A-</b> 5 |

| APPENDIX B  | USYNRT DESCRIPTION                          |             |

| APPENDIX C  | IC DESCRIPTIONS                             |             |

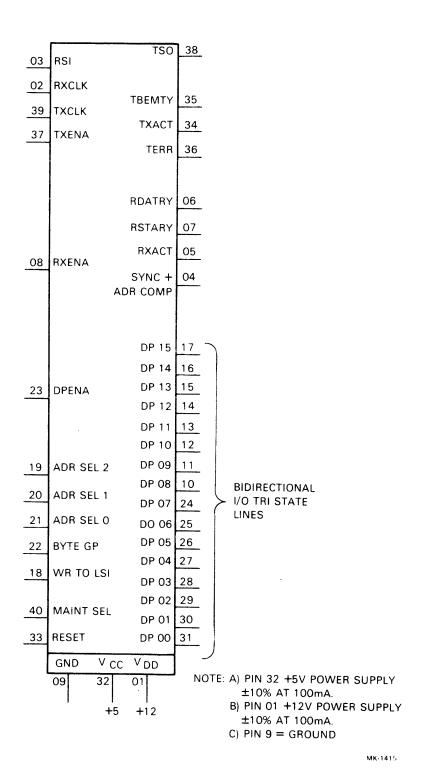

| C.1         | GENERAL                                     | C-1         |

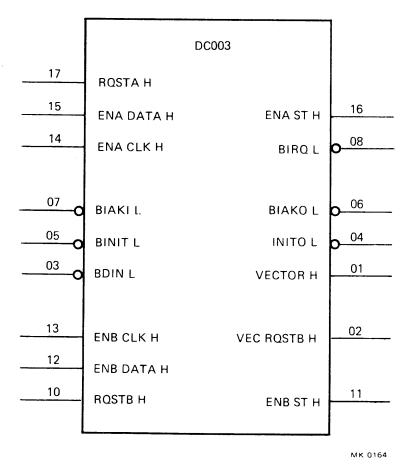

| C.2         | DC003 INTERRUPT CHIP                        |             |

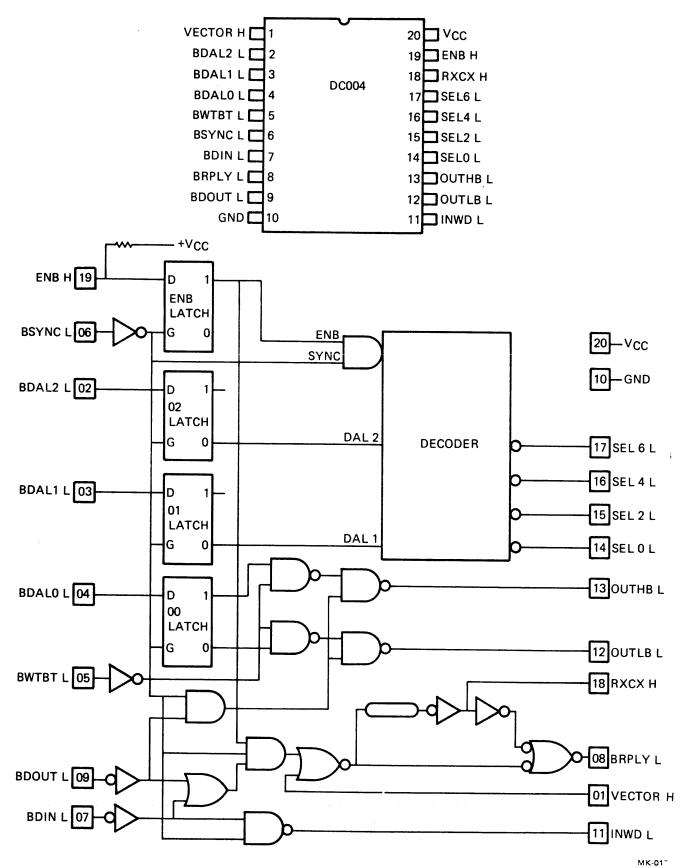

| C.3         | DC004 PROTOCOL CHIP                         | C-3         |

| C.4         | DC005 BUS TRANSCEIVER CHIP                  | C-3         |

| C.5         | 26LS32 QUAD DIFFERENTIAL LINE RECEIVER      | C-6         |

| C.6         | 8640 UNIBUS RECEIVER                        | C-6         |

| C.7         | 8881 NAND                                   |             |

| C.8         | 9636A DUAL LINE DRIVER                      |             |

| C.9         | 9638 DUAL DIFFERENTIAL LINE DRIVER          | C-6         |

| APPENDIX D  | PROGRAMMING EXAMPLES                        |             |

| GLOSSARY    |                                             |             |

|             |                                             |             |

|             |                                             |             |

|             |                                             |             |

|             |                                             |             |

# **ILLUSTRATIONS**

| Figure No. | Title                                                  | Page |

|------------|--------------------------------------------------------|------|

| 1-1        | DPV11 System                                           | 1-1  |

| 2-1        | DPV11 Jumper Locations                                 | 2-4  |

| 2-2        | H3259 Turn-Around Test Connector                       | 2-8  |

| 2-3        | RS-423-A with H3259 Test Connector                     |      |

| 2-4        | H3260 On-Board Test Connector                          |      |

| 3-1        | DPV11 Register Configurations and Bit Assignments      |      |

| 3-2        | Receive Control and Status Register (RXCSR) Format     |      |

| 3-3        | Receive Data and Status Register (RDSR) Format         |      |

| 3-4        | Parameter Control Sync/Address Register (PCSAR) Format |      |

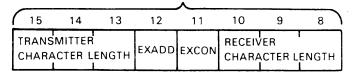

| 3-5        | Parameter Control and Character Length Register        |      |

|            | (PCSCR) Format                                         | 3-13 |

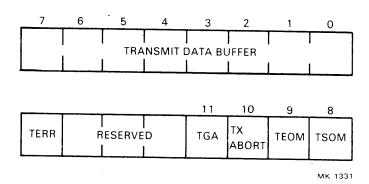

| 3-6        | Transmit Data and Status Register (TDSR) Format        |      |

| A-1        | Typical XXDP+/Diagnostic Supervisor Memory Layout      |      |

# ILLUSTRATIONS (Cont)

| Figure No. | Title                                                        | Page |

|------------|--------------------------------------------------------------|------|

| B-1        | Terminal Connection Identification Diagram                   |      |

|            | (2112517-0-0 Variation)                                      | B-2  |

| B-2        | 5025 Internal Register Bit Map (2112517-0-0 Variation)       | B-3  |

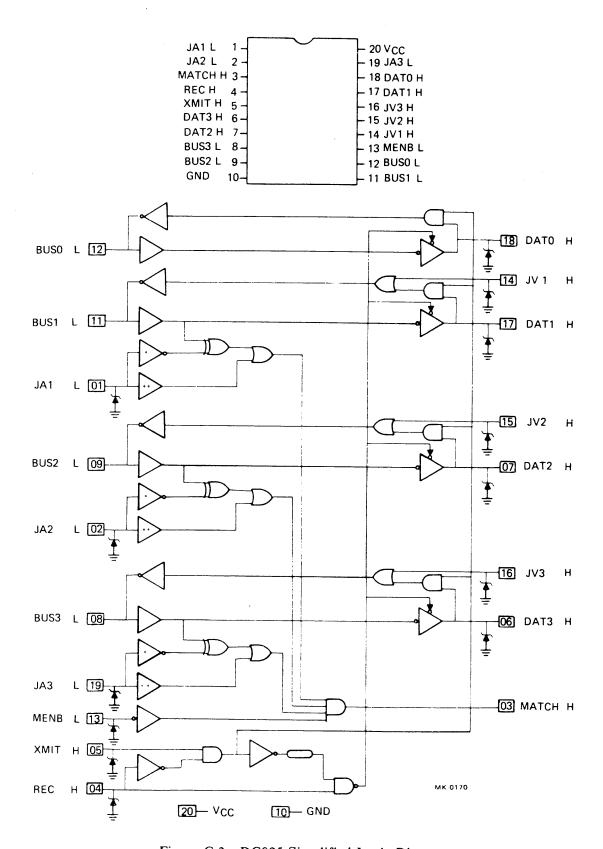

| C-1        | DC003 Logic Symbol                                           | C-1  |

| C-2        | DC004 Simplified Logic Diagram                               |      |

| C-3        | DC005 Simplified Logic Diagram                               |      |

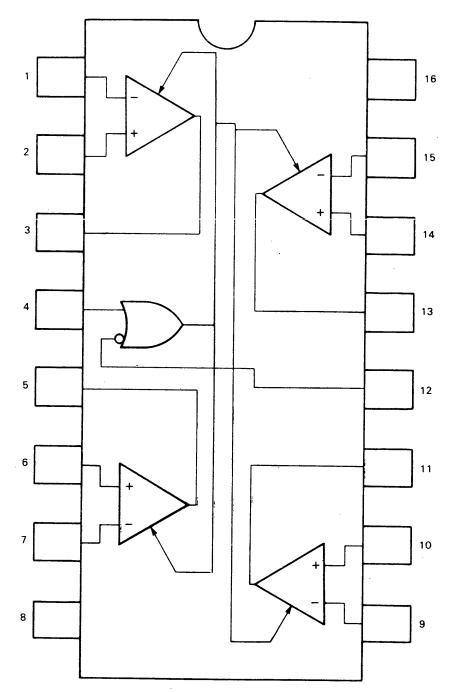

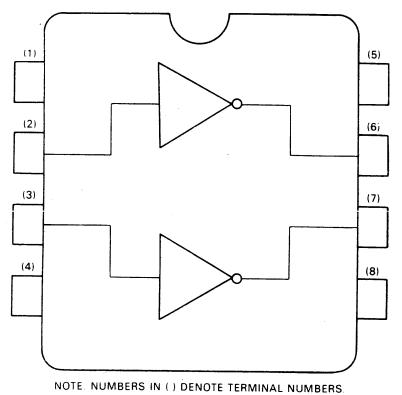

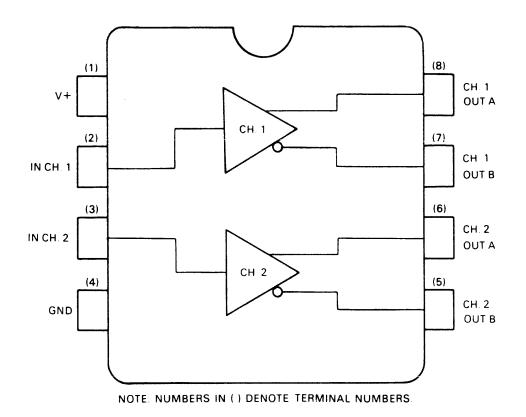

| C-4        | 26LS32 Terminal Connection Diagram and Terminal              |      |

|            | Indentification                                              |      |

| C-5        | 8640 Equivalent Logic Diagram                                |      |

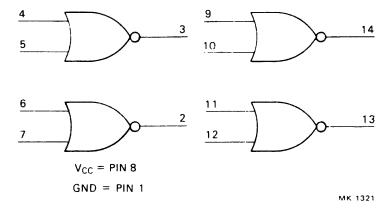

| C-6        | 8881 Pin Identification                                      |      |

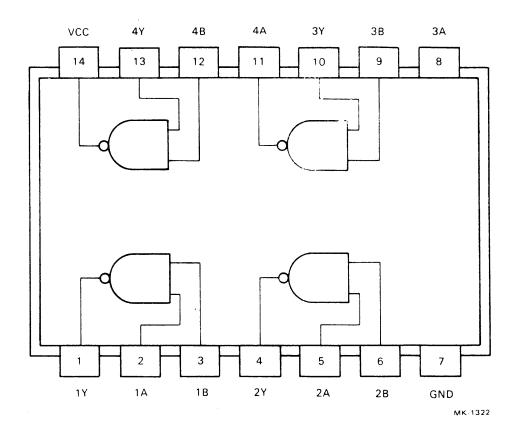

| C-7        | 9636A Logic Diagram and Terminal Identification              |      |

| C-8        | 9638 Logic Diagram and Terminal Identification               |      |

|            | TABLES                                                       |      |

| Table      |                                                              | _    |

| No.        | Title Page                                                   | Page |

| 2-1        | Configuration Sheet                                          | 2-1  |

| 2-2        | Vector Address Selection                                     | 2-5  |

| 2-3        | Device Address Selection                                     | 2-€  |

| 2-4        | Voltage Requirements                                         | 2-7  |

| 2-5        | H3259 Test Connections                                       |      |

| 3-1        | DPV11 Registers                                              | 3-1  |

| 3-2        | Receive Control and Status Register (RXCSR) Bit              |      |

|            | Assignments                                                  | 3-5  |

| 3-3        | Receive Data and Status Register (RDSR) Bit Assignments      | 3-8  |

| 3-4        | Parameter Control Sync/Address Register (PCSAR)              |      |

|            | Bit Assignments                                              | 3-11 |

| 3-5        | Parameter Control and Character Length Register              |      |

|            | (PCSCR) Bit Assignments                                      | 3-14 |

| 3-6        |                                                              |      |

| C-1        | Transmit Data and Status Register (TDSK) Bit Assignments     |      |

| ~ ·        | Transmit Data and Status Register (TDSR) Bit Assignments     |      |

| C-2        | DC003 Pin/Signal Descriptions  DC004 Pin/Signal Descriptions |      |

# **PREFACE**

This manual is intended to provide an introduction to the DPV11 Interface and present the information required by the user for configuration, installation and operation.

It contains the following categories of information.

- General description including features, specifications, and configurations

- Installation

- Programming

The manual also contains four appendixes which include diagnostic information, integrated circuit descriptions, and programming examples.

The DPV11 Field Maintenance Print Set (MP00919) contains useful additional information.

# CHAPTER 1 INTRODUCTION

#### 1.1 SCOPE

This chapter contains introductory information about the DPV11. It includes a general description, and a brief overview of the DPV11 operation, features, general specifications, and configurations.

#### 1.2 DPV11 GENERAL DESCRIPTION

The DPV11 is a serial synchronous line interface for connecting an LSI-11 bus to a serial synchronous modem that is compatible with EIA RS-232-C interface standards and EIA RS-423-A and RS-422-A electrical standards. EIA RS-422-A compatibility is provided for use in local communications only (timing and data leads only). The DPV11 is intended for character-oriented protocols such as BISYNC, byte count-oriented protocols such as DDCMP, or bit-oriented data communication protocols such as SDLC. The DPV11 does not provide automatic error generating and checking for BISYNC.

The DPV11 consists of one double-height module and may be connected to an EIA RS-232-C modem by a BC26L-25 (RS-232-C) cable.

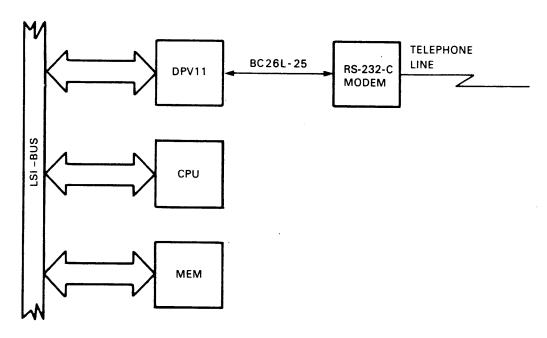

The DPV11 is a bus request device only and must rely on the system software for service. Interrupt control logic generates requests for the transfer of data between the DPV11 and the LSI-11 memory by means of the LSI-11 bus. (Figure 1-1 shows the DPV11 system.)

MK-1320

Figure 1-1 DPV11 System

#### 1.3 DPV11 OPERATION

The DPV11 is a double-buffered program interrupt interface that provides parallel-to-serial conversion of data to be transmitted and serial-to-parallel conversion of received data. The DPV11 can operate at speeds up to 56K b/s.\* It has five 16-bit registers which can be accessed in word or byte mode. These registers are assigned a block of four contiguous LSI-11 bus word addresses that start on a boundary with the low-order three bits being zeros. This block of addresses is jumper-selectable and may be located anywhere between 160000<sub>8</sub> and 177776<sub>8</sub>. Two of these registers share the same address. One is accessed during a read from the address, the other during a write to the address. For a detailed description of each of the five registers, refer to Chapter 3. These registers are used for status and control information as well as data buffers for both the transmitter and receiver portions of the DPV11.

#### 1.4 DPV11 FEATURES

Features of the DPV11 include:

- Full-duplex or half-duplex operation

- Double-buffered transmitter and receiver

- EIA RS-232-C compatibility

- All EIA RS-449 Category I modem control

- Partial Category II modem control to include incoming call, test mode, remote loopback, and local loopback

- Program interrupt on transitions of modem control signals

- Operating speeds up to 56K b/s (may be limited by software or CPU memory)

- Software-selectable diagnostic loopback

- Operation with bit-, byte count-, or character-oriented protocols

- Internal cyclic redundancy check (CRC) character generation and checking (not usable with BISYNC)

- Internal bit-stuff and detection with bit-oriented protocols.

- Programmable sync character, sync insertion, and sync stripping with byte count-oriented protocols.

- Recognition of secondary station address with bit-oriented protocols.

#### 1.5 GENERAL SPECIFICATIONS

This paragraph contains environmental, electrical, and performance specifications for the DPV11.

# 1.5.1 Environmental Specifications

The DPV11 is designed to operate in a Class C environment as specified by DEC Standard 102 (extended).

Operating Temperature

5° C (41° F) to 60° C (140° F)

Relative Humidity

10% to 90% with a max. wet bulb temperature of 28° C (82°

F) and a min. dew point of 2° C (36° F)

<sup>\*</sup>The actual speed realized may be significantly less because of limitations imposed by the software and/or CPU memory refresh.

# 1.5.2 Electrical Specifications

The DPV11 requires the following voltages from the LSI-11 bus for proper operation.

```

+12 V at 0.30 A max. (0.15 A typical)

+5 V at 1.2 A max. (0.92 A typical)

```

The interface includes a charge pump to generate a negative voltage required to power the RS-423-A drivers.

The DPV11 presents 1 ac load and 1 dc load to the LSI-11 bus.

#### 1.5.3 Performance Parameters

Performance parameters for the DPV11 are listed as follows.

Operating Mode Full or half-duplex

Data Format Synchronous BISYNC, DDCMP, and SDLC

Character Size Program-selectable (5–8 bits with character-oriented

protocols and 1-8 bits with bit-oriented protocols)

Max. Configuration 16 DPV11 modules per LSI-11 bus

Max. Distance 15 m (50 ft) for RS-232-C. 61 m (200 ft) for RS-423-

A/RS-422-A (Distance is directly dependent on speed, and 200 ft is a suggested average. See RS-449 specifica-

tion for details.)

Max. Serial Data Rates 56K b/s (May be less because of software and memory

refresh limitations.)

#### 1.6 DPV11 CONFIGURATIONS

There are two DPV11 configurations, the DA and the DB.

DPV11-DA

Unbundled version consists of:

M8020 module

DPV11 Maintenance Reference Card (EK-DPV11-CG)

DPV11-DB

Bundled version consists of:

M8020 module

H3259 turn-around connector

BC26L-25 cable

DPV11 User Manual (EK-DPV11-UG)

DPV11 Maintenance Reference Card (EK-DPV11-CG)

LIB kit (ZJ314-RB)

Field Maintenance Print Set (MP00919)

Turn-around connectors, cables and documentation may be purchased separately.

#### 1.7 EIA STANDARDS OVERVIEW (RS-449/RS-232-C)

The most common interface standard used in recent years has been the RS-232-C. However, this standard has serious limitations for use in modern data communication systems. The most critical limitations are in speed and distance.

For this reason, RS-449 standard has been developed to replace RS-232-C. It maintains a degree of compatibility with RS-232-C to accommodate an upward transition to RS-449.

The most significant difference between RS-232-C and RS-449 is in the electrical characteristics of signals used between the data communication equipment (DCE) and the data terminal equipment (DTE). The RS-232-C standard uses only unbalanced circuits, while the RS-449 uses both balanced and unbalanced electrical circuits. The specifications for the types of electrical circuits supported by RS-449 are contained in EIA standards RS-422-A for balanced circuits and RS-423-A for unbalanced circuits. These new standards permit much greater transmission speed and will allow greater distance between DTE and DCE. The maximum transmission speeds supported by RS-422-A and RS-423-A circuits vary with cable length; the normal speed limits are 20K b/s for RS-423-A and 2M b/s for RS-422-A, both at 61 m (200 feet).

Another major difference between RS-232-C and RS-449 is that additional leads are needed to support the balanced interface circuits and some new circuit functions. Two new connectors have been specified to accommodate these new leads. One connector is a 37-pin Cinch used in applications requiring secondary channel functions. Some of the new circuits added in RS-449 support local and remote loopback testing, and stand-by channel selection.

# CHAPTER 2 INSTALLATION

#### 2.1 INTRODUCTION

This chapter provides all the information necessary for a successful installation and subsequent checkout of the DPV11. Included are instructions for unpacking and inspection, pre-installation, installation and verification of operation.

# 2.2 UNPACKING AND INSPECTION

The DPV11 is packaged in accordance with commercial packing practices. Remove all packing material and verify that the following are present.

M8020 module H3259 turn-around connector BC26L-25 cable DPV11 User Manual (EK-DPV11-UG) LIB kit (ZJ314-RB) Field Maintenance Print Set (MP00919)

Inspect all parts carefully for cracks, loose components or other obvious damage. Report damages or shortages to the shipper immediately, and notify the DIGITAL representative.

#### 2.3 PRE-INSTALLATION REQUIREMENTS

Table 2-1 (Configuration Sheet) provides a convenient, quick reference for configuring jumpers.

**Table 2-1 Configuration Sheet**

| (W1-W2) Driver        | Attenuation Jumper       |                      |                                                                                                |  |  |  |  |

|-----------------------|--------------------------|----------------------|------------------------------------------------------------------------------------------------|--|--|--|--|

| Driver                | Normal*<br>Configuration | Alternate*<br>Option | Description                                                                                    |  |  |  |  |

| Terminal<br>Timing    | W1 to W2                 | Not connected        | Bypasses attenuation resistor.  Jumper must be removed for certain modems to operate properly. |  |  |  |  |

| (W3-W11) Inter        | face Selection Jumpers   |                      |                                                                                                |  |  |  |  |

| Input<br>Signals      | Normal*<br>Configuration | Alternate*<br>Option | Description                                                                                    |  |  |  |  |

| SQ/TM<br>(PCSCR-5)    | W5 to W6                 |                      | Signal quality                                                                                 |  |  |  |  |

| (I CSCR-3)            |                          | W7 to W6             | Test mode                                                                                      |  |  |  |  |

| DM (DSR)<br>(RXCSR-9) | Not connected            | W10 to W9            | Data mode return for RS-422-A                                                                  |  |  |  |  |

<sup>\*</sup>Normal configuration is typically RS-423-A compatible. Alternate option is typically RS-422-A compatible.

Table 2-1 Configuration Sheet (Cont)

# (W3-W11) Interface Selection Jumpers (Cont)

| Output<br>Signals  | Normal*<br>Configuration | Alternate*<br>Option | Description                    |  |  |  |

|--------------------|--------------------------|----------------------|--------------------------------|--|--|--|

| SF/RL<br>(RXCSR-0) | W3 to W4                 |                      | Select frequency               |  |  |  |

| (                  |                          | W5 to W3             | Remote loopback                |  |  |  |

| Local<br>Loopback  | W8 to W9                 | Not connected        | Local loopback                 |  |  |  |

| Loopoack           | Not connected            | W8 to W11            | Local loopback (alternate pin) |  |  |  |

# (W12-W17) Receiver Termination Jumpers

| Receiver          | Normal*<br>Configuration | Alternate*<br>Option | Description                       |  |  |  |  |  |

|-------------------|--------------------------|----------------------|-----------------------------------|--|--|--|--|--|

| Receive Data      | Not connected            | W12 to W13           | Connects terminating resistor for |  |  |  |  |  |

| Send Timing       | Not connected            | W14 to W15           | RS-422-A compatibility            |  |  |  |  |  |

| Receive<br>Timing | Not connected            | W16 to W17           |                                   |  |  |  |  |  |

# (W18-W23) Clock Jumpers

| Function          | Normal*<br>Configuration | Alternate*<br>Option     | Description                                  |  |  |  |

|-------------------|--------------------------|--------------------------|----------------------------------------------|--|--|--|

| NULL MODEM<br>GLK | W20 to W18               |                          | Sets NULL CLK MODEM CLK to 2 kHz.            |  |  |  |

|                   |                          | W21 to W18               | Sets NULL MODEM CLK to 50 kHz.               |  |  |  |

| Clock Enable      | W19 to W21<br>W22 to W23 | W19 to W21<br>W22 to W23 | Always installed except for factory testing. |  |  |  |

# (W24-W28) Data Set Change Jumpers

| Modem Signal<br>Name               | Normal*<br>Configuration | Alternate*<br>Option | Description                                                        |

|------------------------------------|--------------------------|----------------------|--------------------------------------------------------------------|

| Data Mode (DSR)                    | W26 to W24               | Not connected        | Connects the DSCNG flip-flop to the respective modem status signal |

| Clear to Send                      | W26 to W25               | Not connected        | for transition detection.                                          |

| Incoming Call                      | W26 to W27               | Not connected        | Note: W26 is input to DSCNG flip-flop                              |

| Receiver Ready<br>(Carrier Detect) | W26 to W28               | Not connected        |                                                                    |

<sup>\*</sup>Normal configuration is typically RS-423-A compatible. Alternate option is typically RS-422-A compatible. 2-2

Table 2-1 Configuration Sheet (Cont)

#### **Device Address Jumpers**

**A9** GND A12 A11 A10 **A8 A7 A6 A5** A4 **A3** W29 W31 W30 W36 W33 W32 W39 W38 W37 W34 W35

#### NOTE

The address to which the DPV11 is to respond is daisy-chain jumpered to W29 (GND).

#### **Vector Address Jumpers**

D8 D7 D6 D5 D4 D3 Source W43 W42 W41 W40 W44 W45 W46

#### **NOTE**

Vector address to be asserted is daisy-chain jumpered to W46.

#### **NOTE**

Table 2-1 shows the recommended normal and alternate jumpering schemes. Any deviation from these will cause diagnostics to fail and require restrapping for full testing and verification. It is recommended that customer configurations that vary from this scheme not be contractually supported.

Prior to installing the DPV11, perform the following tasks.

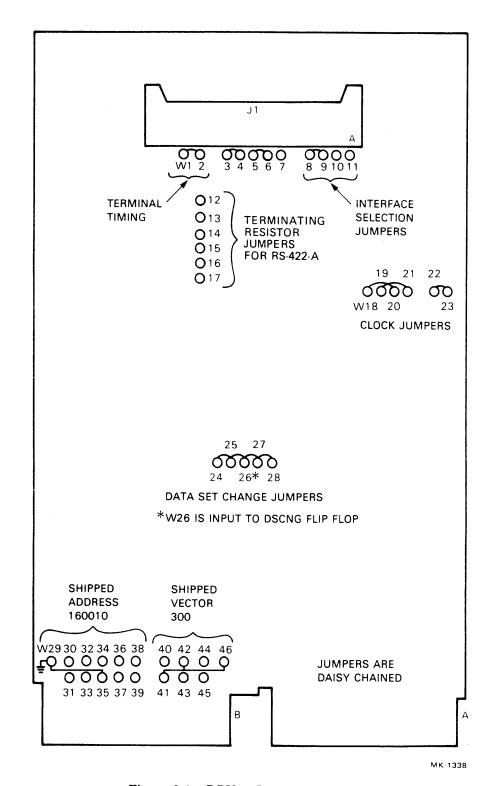

1. Verify that the following modem interface wire-wrap jumpers are installed (Figure 2-1).

W26 to W25 to W24 to W28 to W27

W22 to W23 and W19 to W21

W18 to W20

W5 to W6

W3 to W4

W8 to W9

W1 to W2

This is the normal/RS-423-A shipped configuration. Some of these jumpers may be changed when the module is connected to external equipment for a specific application. The NULL MODEM CLK is set to 2 kHz as shipped.

- 2. Based on the LSI-11 bus floating vector scheme or user requirements, determine the vector address for the specific DPV11 module being installed and configure W40 through W46 accordingly (Table 2-2).

- 3. Based on the LSI-11 bus floating address scheme or user requirements, determine the device address range for the DPV11 module and configure W30 through W39 accordingly (Table 2-3). Devices may be physically addressed starting at 160000 and continuing through 177776; however, there may be some software restrictions. The normal addressing convention is as shown in Table 2-3.

Figure 2-1 DPV11 Jumper Locations

Table 2-2 Vector Address Selection

DPV11 (M8020) VECTOR ADDRESSING

| MSB |    |    |    |    |               |   |             |                            |                                       |      |     |             |     |                                                        | LSB                       |  |

|-----|----|----|----|----|---------------|---|-------------|----------------------------|---------------------------------------|------|-----|-------------|-----|--------------------------------------------------------|---------------------------|--|

| 15  | 14 | 13 | 12 | 11 | 10            | 9 | 8           | 7                          | 6                                     | 5    | 4   | 3           | 2   | 1                                                      | 0                         |  |

| 0   | 0  | 0  | 0  | 0  | 0             | 0 |             |                            | JUMI                                  | PERS |     |             | 1/0 | 0                                                      | . 0                       |  |

| -   |    |    |    |    |               |   |             | <br>                       |                                       |      |     |             |     |                                                        |                           |  |

|     |    |    |    |    | UMPE<br>IUMBE |   | W43         | W42                        | W41                                   | W40  | W44 | W45         |     |                                                        | TOR<br>RESS               |  |

|     |    |    |    |    |               |   | ×<br>×<br>× | x<br>x<br>x<br>x<br>x<br>x | × × × × × × × × × × × × × × × × × × × | ×××  | ××× | ×<br>×<br>× |     | 30<br>31<br>32<br>33<br>34<br>35<br>36<br>37<br>40<br> | 00<br>0<br>20<br>30<br>40 |  |

"X" INDICATES A CONNECTION TO W46.

W46 IS THE SOURCE JUMPER FOR THE VECTOR ADDRESS

JUMPERS ARE DAISY CHAINED.

MK-1341

Table 2-3 Device Address Selection

DPV11-XX (M8020) DEVICE ADDRESSING

| MSB |               |    |            |           |           |      |     |        |     |             |           |             |                                 |                                                                          | LSB      |

|-----|---------------|----|------------|-----------|-----------|------|-----|--------|-----|-------------|-----------|-------------|---------------------------------|--------------------------------------------------------------------------|----------|

| 15  | 14            | 13 | 12         | 11        | 10        | 9    | 8   | 7      | 6   | 5           | 4         | 3           | 2                               | 1                                                                        | 0        |

| 1   | 1             | 1  | -          |           |           |      | JUN | IPERS  |     |             |           |             | 0                               | 0                                                                        | 0        |

|     |               |    | 1 .<br>1 . | <br> <br> | <br> <br> | <br> | _   | 1<br>1 | 1   | Ξ           | <br> <br> | <br>        | <br> <br> <br>                  | <u> </u>                                                                 | <u> </u> |

|     | JMPEI<br>JMBE |    | W31        | W30       | W36       | W33  | W32 | W39    | W38 | W37         | W34       | W35         |                                 | EVICE<br>DDRES                                                           |          |

|     |               |    |            |           |           |      | ××  | ×      | ×   | ×<br>×<br>× | ×××       | x<br>x<br>x | 7<br>7<br>7<br>7<br>7<br>7<br>7 | 60010<br>60020<br>60030<br>60060<br>60060<br>60070<br>60100<br><br>60300 |          |

|     |               |    |            |           |           |      | ×   | ×      |     |             |           |             |                                 | <br>60600                                                                | - 1      |

|     |               |    |            |           |           | ×    | ×   | ×      | Х   |             |           |             |                                 | 60700<br><br>61000                                                       | l        |

|     |               |    |            |           | x         |      |     |        |     |             |           |             | 76                              | <br>52000<br>                                                            |          |

|     |               |    |            | ×         | ×         | ×    |     |        |     |             |           |             |                                 | 3000<br><br>54000                                                        |          |

"X" INDICATES A CONNECTION TO W29. W29 IS TIED TO GROUND. JUMPERS ARE DAISY CHAINED.

MK-1339

# 2.4 INSTALLATION

The DPV11 can be installed in any LSI-11 bus-compatible backplane such as H9270. LSI-11 configuring rules must be followed. Proceed with the installation as follows. For additional information refer to PDP-11/03 User Manual EK-LSI11-TM or LSI-11 Installation Guide EK-LSI11-IG.

1. Configure the address and vector jumpers at this time if they have not been previously done (Paragraph 2.3).

WARNING Turn all power OFF. 2. Connect the female Berg connector on the BC26L-25 cable to J1 on the M8020 module † and plug the module into a dual LSI-11 bus slot of the backplane.

#### **CAUTION**

Insert and remove modules slowly and carefully to avoid snagging module components on the card guides.

- 3. Connect the H3259<sup>†</sup> turn-around connector to the EIA connection on the BC26L-25 cable. The jumper W1 on the H3259 turn-around connector must be removed.

- 4. Perform resistance checks from backplane pin AA2 (+5 V) to ground and from AD2 (+12 V) to ground to ensure that there are no shorts on the M8020 module or backplane.

- 5. Turn system power on.

- 6. Check the voltages to ensure that they are within the specified tolerances (Table 2-4). If voltages are not within specified tolerances, replace the associated regulator (H780 P.S.)

**Table 2-4** Voltage Requirements

| Voltage | Max.  | Min.   | Backplane Pin |

|---------|-------|--------|---------------|

| +5 V    | +5.25 | +4.75  | AA2           |

| +12 V   | 12.75 | +11.25 | AD2           |

# 2.4.1 Verification of Hardware Operation

The M8020 module is now ready to be tested by running the CVDPV\* diagnostic. Additional information on the DPV11 diagnostics is contained in Appendix A. Proceed as follows.

#### NOTE

The \* represents the revision level of the diagnostic.

1. Load and run CVDPV\*. Three consecutive error-free passes of this test is the minimum requirement for a successful run. If this cannot be achieved, check the following.

Board seating

Jumper connections

Cable connection

Test connector

If a successful run is still unachievable, corrective maintenance is required.

2. Load and run the DEC/X11 System Exerciser configured to test the number of DPV11s in the system.

Each DEC/X11 CXDPV module will test up to eight consecutively addressed DPV11s.

CXDPV uses a software switch register. Refer to the *DEC/X11 Cross-Reference* (AS-F055C-MC) for switch register utilization.

<sup>†</sup> If a BC26L-25 cable and H3259 turn-around connector are not available, an on-board test connector (H3260) can be ordered separately. See Paragraph 2.5.

The DEC/X11 System Exerciser is designed to achieve maximum contention with all devices that make up the system configuration. It is within this environment that the CXDPV module runs. Its intent is to isolate DPV11s which adversely affect the system operation.

For information on configuring and running the DEC/X11 System Exerciser, refer to DEC/X11 User Manual (AS-F0503B-MC) and DEC-X11 Cross Reference (AS-F055C-MC).

## 2.4.2 Connection to External Equipment/Link Testing

The DPV11 is now ready for connection to external equipment.

If the DPV11 is being connected to a synchronous modem, remove the H3259 connector and install the EIA connection of the BC26L-25 cable into the connector on the modem.

Configure jumpers W1-W28 in accordance with operating requirements (Table 2-1).

Load and run DCLT (CVCLH\*) if a full link is available. This will check the final configuration and isolate failures to the CPU, the communications link, or the modem.

If the connection to external equipment uses RS-422-A, the user must provide the cable and test support.

#### 2.5 TEST CONNECTORS

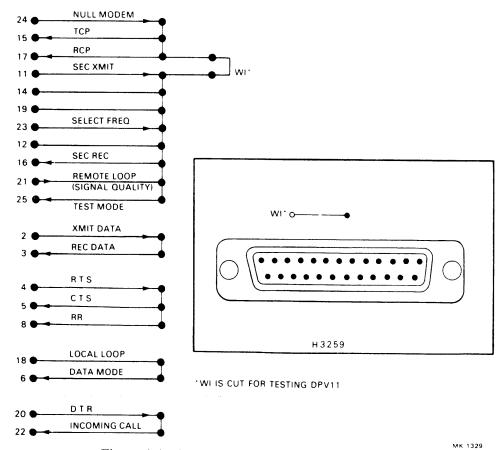

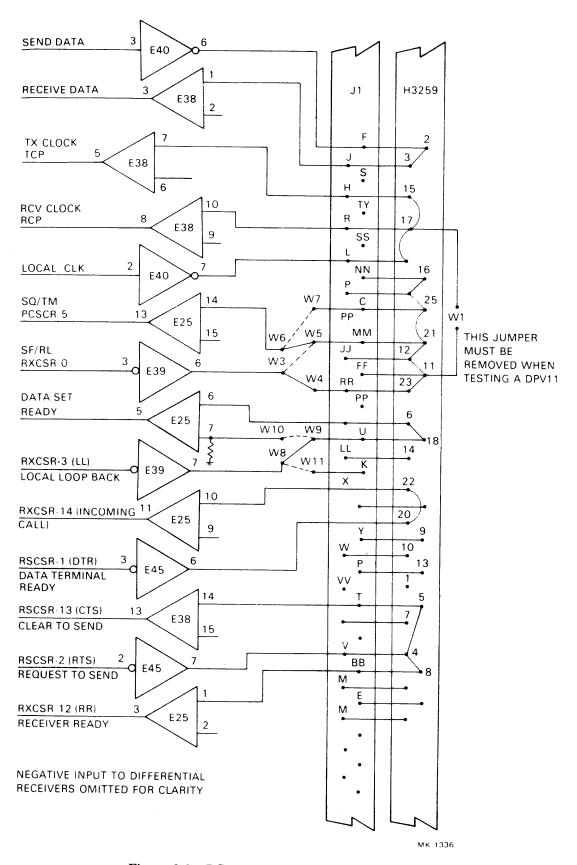

The only test connector provided with the DPV11 is the H3259 turn-around connector (Figure 2-2). Table 2-5 and Figure 2-3 show the relationship between pin numbers, signal names and register bits when the H3259 is connected by means of the BC26L-26 cable to the M8020 module.

Figure 2-2 H3259 Turn-Around Test Connector

Table 2-5 H3259 Test Connections

| From                                                |                  | То            |               |                  |                                                                        |

|-----------------------------------------------------|------------------|---------------|---------------|------------------|------------------------------------------------------------------------|

| Signal Name                                         | Pin No.<br>H3259 | Pin No.<br>J1 | Pin No.<br>J1 | Pin No.<br>H3259 | Signal Name                                                            |

| SEND DATA                                           | 2                | F             | J             | 3                | RECEIVE DATA                                                           |

| REQUEST TO SEND<br>(RTS) (RXCSR-2)                  | 4                | V             | вв&т          | 5&8              | CLEAR TO SEND<br>(CTS)(RXCSR-13),<br>RECEIVER READY<br>(RR) (RXCSR-12) |

| LOCAL LOOPBACK<br>(LL) (RXCSR-3)                    | 18               | U             | Z             | 6                | DATA MODE<br>(DM) (RXCSR-9)                                            |

| SELECT FREQ/REMOTE<br>LOOPBACK<br>(SF/RL) (RXCSR-0) | 23/21            | RR/MM         | MM/C          | 21/25            | SIGNAL QUALITY/<br>TEST MODE<br>(SQ/TM) (PCSCR-5)                      |

| NULL MODEM                                          | 24               | L             | N&R           | 15&17            | RCV CLOCK<br>TX CLOCK                                                  |

| DATA TERMINAL<br>READY (DTR)<br>(RXCSR-1)           | 20               | DD            | x             | 22               | INCOMING CALL<br>(IC) (RXCSR-14)                                       |

The following accessories are available for interfacing and may be ordered separately.

- BC26L-X cable. Available in lengths of .3, 1.8, 2.4, 3.0, 3.6, 6.1, and 7.6 meters (1, 6, 8, 10, 12, 20 and 25 feet). When ordering, the dash number indicates the desired cable length in feet; e.g., BC26L-25 or BC26L-1.

- H3259 cable turn-around connector

- H856 Berg connector. Includes H856 Berg connector and 40 pins. Crimping tools are available from:

Berg Electronics, Inc. New Cumberland, PA 17070

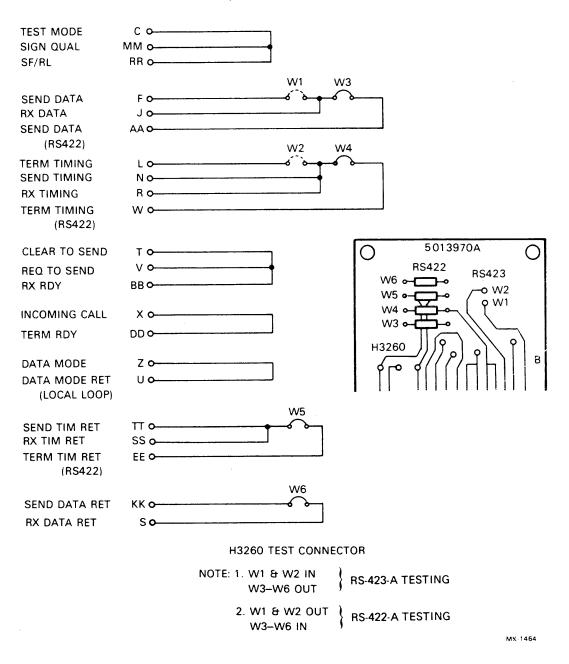

• H3260 on-board test connector (includes RS-422-A testing)

The H3260 on-board test connector (Figure 2-4) may be used to test the M8020 circuitry in its entirety. RS-422-A circuitry is not tested with the H3259 cable turn-around connector. The H3260 on-board test connector is shipped configured for testing RS-422-A. It may be configured to test RS-422-A or RS-423-A as follows.

| RS-422-A                     | RS-423-A                  |

|------------------------------|---------------------------|

| W1-W2 out<br>W3-W6 installed | W1-W2 installed W3-W6 out |

The connector is installed into J1 with the jumper side up.

Since the H3260 on-board test connector does not test the cable, it is recommended that the DPV11 be tested with a turn-around connector at the modem end of the cable if possible.

Figure 2-3 RS-423-A with H3259 Test Connector

Figure 2-4 H3260 On-Board Test Connector

# CHAPTER 3 REGISTER DESCRIPTIONS AND PROGRAMMING INFORMATION

#### 3.1 INTRODUCTION

This chapter describes the bit assignments and programming considerations for the DPV11. Some typical start and receive sequences for both bit- and character-oriented protocols are included.

#### 3.2 DPV11 REGISTERS AND DEVICE ADDRESSES

The five registers used in the DPV11 are shown in Table 3-1. Note that two of the registers (PCSAR and RDSR) have the same address. This does not constitute a conflict, however, because the PCSAR is a write-only register and the RDSR is a read-only register. These five registers occupy eight contiguous byte addresses which begin on a boundary where the low-order three bits are zero, and can be located anywhere between 160000<sub>8</sub> and 177776<sub>8</sub>.

Table 3-1 DPV11 Registers

| Register Name                             | Mnemonic | Address | Comments                                  |

|-------------------------------------------|----------|---------|-------------------------------------------|

| Receive Control and Status                | RXCSR    | 16xxx0  | Word or byte* addressable.<br>Read/write. |

| Receive Data and Status                   | RDSR**   | 16xxx2  | Word or byte* addressable. Read-only.     |

| Parameter Control Sync/Address            | PCSAR**  | 16xxx2  | Word or byte addressable.<br>Write-only.† |

| Parameter Control and Character<br>Length | PCSCR‡   | 16xxx4  | Word or byte addressable.<br>Read/write.  |

| Transmit Data and Status                  | TDSR**   | 16xxx6  | Word or byte addressable. Read/write.     |

<sup>\*</sup> Reading either byte of these registers, clears data and certain status bits in other bytes. See Paragraphs 3.3.1 and 3.3.2.

The DPV11 uses a universal-synchronous receiver/transmitter (USYNRT) chip which accounts for a large portion of the DPV11's functionality. The USYNRT provides complete serialization, deserialization and buffering of data to and from the modem.

<sup>\*\*</sup> Registers contained within the USYNRT.

<sup>†</sup> It is not possible to do bit set or bit clear instructions on this register.

<sup>‡</sup>The high byte of this register is internal to the USYNRT.

Most of the DPV11 registers are internal to the USYNRT. Only the receiver control and status register (RXCSR) and the low byte of the parameter control and character length register (PCSCR) are external.

#### NOTE

When using the special space sequence function, all registers internal to the USYNRT must be written in byte mode.

# 3.3 REGISTER BIT ASSIGNMENTS

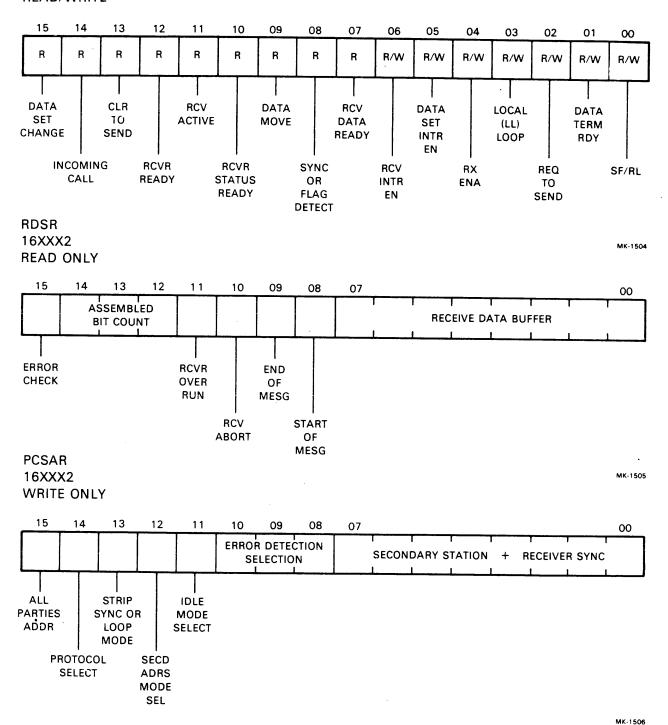

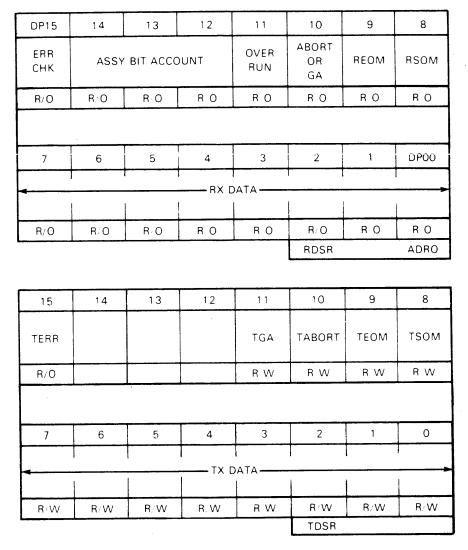

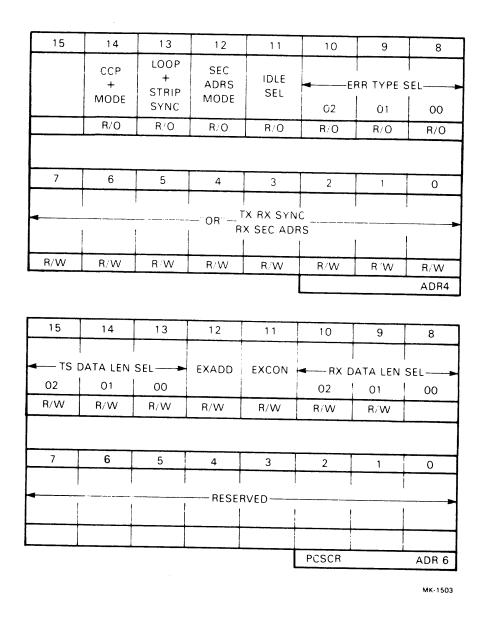

Bit assignments for the five DPV11 registers are shown in Figure 3-1. Paragraphs 3.3.1-3.3.5 provide a description of each register using a bit assignment illustration and an accompanying table with a detailed description of each bit.

# 3.3.1 Receive Control and Status Register (RXCSR) (Address 16xxx0)

Figure 3-2 shows the format for the receive control and status register (RXCSR). Table 3-2 is a detailed description of the register. This register is external to the USYNRT.

#### NOTE

The RXCSR can be read in either word or byte mode. However, reading either byte resets certain status bits in both bytes.

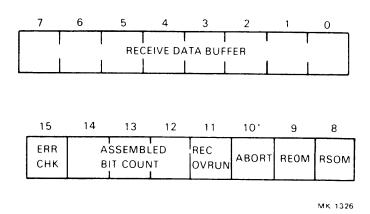

# 3.3.2 Receive Data and Status Register (RDSR) (Address 16xxx2)

Figure 3-3 show the format for the receive data and status register (RDSR). It is a read-only register and shares its address with the parameter control sync/address register (PCSAR) which is write-only. Table 3-3 is a detailed description of the RDSR.

#### NOTE

The RDSR can be read in either word or byte mode. However, reading either byte resets data and certain status bits in both bytes of this register as well as bits 7 and 10 of the RXCSR.

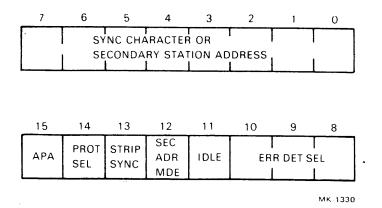

# 3.3.3 Parameter Control Sync/Address Register (PCSAR) (Address 16xxx2)

The parameter control sync/address register (PCSAR) is a write-only register which can be written in either byte or word mode. Figure 3-4 shows the format and Table 3-4 is a detailed description of the PCSAR. This register shares its address with the RDSR.

### NOTE

Bit set (BIS) and bit clear (BIC) instructions cannot be executed on the PCSCR, since they execute using a read-modify-write sequence.

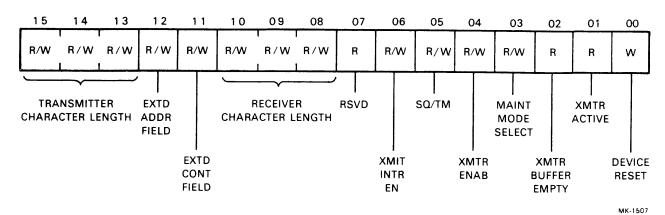

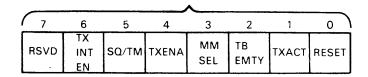

# 3.3.4 Parameter Control and Character Length Register (PCSCR) (Address 16xxx4)

The parameter control and character length register (PCSCR) can be read from or written into in either word or byte mode. The low byte of this register is external to the USYNRT and the high byte is internal. Figure 3-5 shows the format and Table 3-5 is a detailed description of the PCSCR.

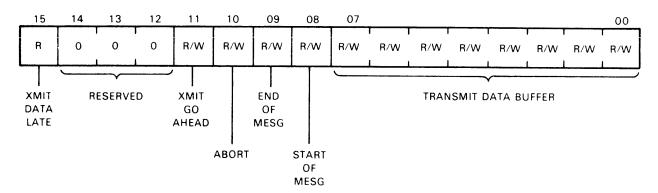

# 3.3.5 Transmit Data and Status Register (TDSR) (Address 16xxx6)

The format for the transmit data and status register (TDSR) is shown in Figure 3-6 and Table 3-6 is a detailed description. The TDSR is a read/write register which can be accessed in either word or byte mode with no restrictions. All bits can be read from or written into and are reset by Device Reset or Bus INIT except where noted.

RXCSR 16XXX0 READ/WRITE

Figure 3-1 DPV11 Register Configurations and Bit Assignments (Sheet 1 of 2)

# PCSCR 16XXX4 READ/WRITE

TDSR 16XXX6 READ/WRITE

MK-1508

Figure 3-1 DPV11 Register Configurations and Bit Assignments (Sheet 2 of 2)

| 7            | 6          | 5          | 4         | 3         | 2      | 1  | 0     |

|--------------|------------|------------|-----------|-----------|--------|----|-------|

| RDAT<br>RY** | RX<br>ITEN | DS<br>ITEN | RX<br>ENA | LL        | RTS    | TR | SF/RL |

| 15           | 14         | 13         | 12        | 11        | 10     | 9  | 8     |

| DS.          | IC         | CTS        | RR        | RX<br>ACT | RSTA** | DM | SFD   |

· THIS BIT IS RESET BY READING EITHER BYTE OF THIS REGISTER.

.. THESE BITS ARE RESET BY READING EITHER BYTE OF RSDR

MK 132

Figure 3-2 Receive Control and Status Register (RXCSR) Format

Table 3-2 Receive Control and Status Register (RXCSR) Bit Assignments

| Bit | Name                       | Description                                                                                                                                                                                                                                                           |

|-----|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15  | Data Set Change<br>(DSCNG) | This bit is set when a transition occurs on any of the following modem control lines:                                                                                                                                                                                 |

|     |                            | Clear to Send Data Mode Receiver Ready Incoming Call                                                                                                                                                                                                                  |

|     |                            | Transition detectors for each of these four lines can be disabled by removing the associated jumper.                                                                                                                                                                  |

|     | ·                          | Data Set Change is cleared by reading either byte of the RXCSR or by Device Reset or Bus INIT.                                                                                                                                                                        |

|     |                            | Data Set Change causes a receive interrupt if DSITEN (bit 5) and RXITEN (bit 6) are both set.                                                                                                                                                                         |

| 14  | Incoming Call (IC)         | This bit reflects the state of the modem Incoming Call line. Any transition of this bit causes Data Set Change bit (bit 15) to be asserted unless the Incoming Call line is disabled by removing its jumper. This bit is read-only and cannot be cleared by software. |

| 13  | Clear to Send<br>(CTS)     | This bit reflects the state of the Clear to Send line of the modem. Any transition of this line causes Data Set Change (bit 15) to be set unless the jumper enabling the Clear to Send signal is removed.                                                             |

|     |                            | Clear to Send is a program read-only bit and cannot be cleared by software.                                                                                                                                                                                           |

| 12  | Receiver Ready<br>(RR)     | This bit is a direct reflection of modem Receiver Ready lead. It indicates that the modem is receiving a carrier signal. For external maintenance loopback, this signal must be high. If the line is open, RR is pulled high by the circuitry.                        |

|     |                            | Any transition of this bit causes Data Set Change (bit 15) to be asserted unless the jumper enabling the Receiver Ready signal is removed.                                                                                                                            |

|     |                            | Receiver Ready is a read-only bit and cannot be cleared by software.                                                                                                                                                                                                  |

| 11  | Receiver Active (RXACT)    | This bit is set when the USYNRT presents the first character of a message to the DPV11. It remains set until the receive data path of the USYNRT becomes idle.                                                                                                        |

|     |                            | Receiver Active is cleared by any of the following conditions: a terminating control character is received in bit-oriented protocol mode; an off transition of Receiver Enable (RXENA) occurs; or Device Reset or Bus INIT is issued.                                 |

Table 3-2 Receive Control and Status Register (RXCSR) Bit Assignments (Cont)

| Bit | Name                               | Description                                                                                                                                                                                                                                                                                                                           |

|-----|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |                                    | Receiver Active is a read-only bit which reflects the state of the USYNRT output pin 5.                                                                                                                                                                                                                                               |

| 10  | Receiver Status<br>Ready (RSTARY)  | This bit indicates the availability of status information in the upper byte of the receive data and status register (RDSR). It is set when any of the following bits of the RDSR are set: Receiver End of Message (REOM); Receiver Overrun (RCV OVRUN); Receiver Abort or Go Ahead (RABORT); Error Check (ERRCHK) if VRC is selected. |

|     |                                    | Receiver Status is cleared by any of the following conditions: reading either byte of the RDSR; clearing Receiver Enable (bit 4 of RXCSR); Device Reset, or Bus Init.                                                                                                                                                                 |

| ;   |                                    | When set, Receiver Status Ready causes a receive interrupt if Receive Interrupt Enable (bit 6) is also set.                                                                                                                                                                                                                           |

|     |                                    | Receiver Status Ready is a read-only bit which reflects the state of USYNRT pin 7.                                                                                                                                                                                                                                                    |

| 9   | Data Mode (DM)<br>(Data Set Ready) | This bit reflects the state of the Data Mode signal from the modem.                                                                                                                                                                                                                                                                   |

|     |                                    | When this bit is set it indicates that the modem is powered on and not in test, talk or dial mode.                                                                                                                                                                                                                                    |

|     |                                    | Any transition of this bit causes the Data Set Change bit (bit 15) to be asserted unless the Data Mode jumper has been removed.                                                                                                                                                                                                       |

|     |                                    | Data Mode is a read-only bit and cannot be cleared by software.                                                                                                                                                                                                                                                                       |

| 8   | Sync or Flag<br>Detect (SFD)       | This bit is set for one clock time when a flag character is detected with bit-oriented protocols, or a sync character is detected with character-oriented protocols.                                                                                                                                                                  |

|     |                                    | SFD is a read-only bit which reflects the state of USYNRT pin 4.                                                                                                                                                                                                                                                                      |

| 7   | Receive Data<br>Ready (RDATRY)     | This bit indicates that the USYNRT has assembled a data character and is ready to present it to the processor.                                                                                                                                                                                                                        |

|     |                                    | If this bit becomes set while Receiver Interrupt Enable (bit 6) is set, a receive interrupt request will result.                                                                                                                                                                                                                      |

|     |                                    | Receive Data Ready is reset when either byte of RDSR is read Receiver Enable (bit 4) is cleared, or Device Reset or Bus INIT is issued.                                                                                                                                                                                               |

|     |                                    | RDATRY is a read-only bit which reflectes the state of US-YNRT pin 6.                                                                                                                                                                                                                                                                 |

Table 3-2 Receive Control and Status Register (RXCSR) Bit Assignments (Cont)

| Bit | Name                                            | Description                                                                                                                                                                                                                                              |

|-----|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6   | Receiver Interrupt<br>Enable (RXITEN)           | When set, this bit allows interrupt requests to be made to the receiver vector whenever RDATRY (bit 7) becomes set.                                                                                                                                      |

|     |                                                 | The conditions which cause the interrupt request are the assertion of Receive Data Ready (bit 7), Receive Status Ready (bit 10), or Data Set Change (bit 15) if DSITEN (bit 5) is also set.                                                              |

|     |                                                 | RXITEN is a program read/write bit and is cleared by Device Reset or Bus INIT.                                                                                                                                                                           |

| 5   | Data Set Interrupt<br>Enable (DSITEN)           | This bit, when set along with RXITEN, allows interrupt requests to be made to the receiver vector whenever Data Set Change (bit 15) becomes set.                                                                                                         |

|     |                                                 | DSITEN is a program read/write bit and is cleared by Device Reset or Bus INIT.                                                                                                                                                                           |

| 4   | Receiver Enable<br>(RXENA)                      | This bit controls the operation of the receive section of the US-YNRT.                                                                                                                                                                                   |

|     |                                                 | When this bit is set, the receive section of the USYNRT is enabled. When it is reset the receive section is disabled.                                                                                                                                    |

|     | ,                                               | In addition to disabling the receive section of the USYNRT, resetting bit 4 reinitializes all but two of the USYNRT receive registers. The two registers not reinitialized are the character length selection buffer and the parameter control register. |

| 3   | Local Loopback<br>(LL)                          | Asserting this bit causes the modem connected to the DPV11 to establish a data loopback test condition.                                                                                                                                                  |

|     |                                                 | Clearing this bit restores normal modem operation.                                                                                                                                                                                                       |

|     |                                                 | Local Loopback is program read/write and is cleared by Device<br>Reset or Bus request to Send is program read/write and is<br>cleared by Device Reset or Bus INIT.                                                                                       |

| 2   | Request to Send<br>(RTS)                        | Setting this bit asserts the Request to Send signal at the modem interface.                                                                                                                                                                              |

|     |                                                 | Request to Send is program read/write and is cleared by Device Reset or Bus INIT.                                                                                                                                                                        |

| 1   | Terminal Ready (TR)<br>(Data Terminal<br>Ready) | When set, this bit asserts the Terminal Ready signal to the modem interface.                                                                                                                                                                             |

|     | Ready)                                          | For auto dial and manual call origination, it maintains the established call. For auto answer, it allows handshaking in response to a Ring signal.                                                                                                       |

Table 3-2 Receive Control and Status Register (RXCSR) Bit Assignments (Cont)

| Bit | Name                                              | Description                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Select Frequency<br>or Remote<br>Loopback (SF/RL) | This bit can be wire-wrap jumpered to function as either select frequency or remote loopback. When jumpered as select frequency (W3 to W4), setting this bit selects the modem's higher frequency band for transmission to the line and the lower frequency band for reception from the line. The clear condition selects the lower frequency for transmission and the higher frequency for reception. |

|     |                                                   | When jumpered for remote loopback (W5 to W3), this bit, when asserted, causes the modern connected to the DPV11 to signal when a remote loopback test condition has been established in the remote modern.                                                                                                                                                                                             |

|     |                                                   | SF/RL is program read/write and is cleared by Device Reset or Bus INIT.                                                                                                                                                                                                                                                                                                                                |

Figure 3-3 Receive Data and Status Register (RDSR) Format

Table 3-3 Receive Data and Status Register (RDSR) Bit Assignments

| Bit                   | Name                                                                                                                                                                                                                                               | Description                                                                                                                                                                            |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Error Check (ERR CHK) | This bit when set, indicates a possible error. It is used in conjunction with the error detection selection bits of the parameter control sync/address register (bits 8-10) to indicate either an error or an all zeros state of the CRC register. |                                                                                                                                                                                        |

|                       |                                                                                                                                                                                                                                                    | With bit-oriented protocols, ERR CHK indicates that a CRC error has occurred. It is set when the Receive End of Message bit (RDSR bit 9) is set.                                       |

|                       |                                                                                                                                                                                                                                                    | With character-oriented protocols ERR CHK is asserted with each data character if all zeros are in the CRC register. The processor must then determine if this indicates an error-free |

Table 3-3 Receive Data and Status Register (RDSR) Bit Assignments (Cont)

| Bit   | Name                            | Description                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|-------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|       |                                 | message or not. If VRC parity is selected, this bit is set for every character which has a parity error.                                                                                                                                                                                                                                                           |  |  |  |  |  |

|       |                                 | ERR CHK is cleared by reading the RDSR, clearing RXENA (RXCSR bit 4), Device Reset or Bus INIT.                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| 14–12 | Assembled Bit<br>Count (ABC)    | Used only with bit-oriented protocols, these bits represent the number of valid bits in the last character of a message. They are all zeros unless the message ends on an unstated boundary. The bits are encoded to represent valid bits as shown below.                                                                                                          |  |  |  |  |  |

|       |                                 | 14 13 12 Number of Valid Bits                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|       |                                 | 0       0       0       All bits are valid         0       0       1       One valid bit         0       1       0       Two valid bits         1       0       0       Four valid bits         1       0       1       Five valid bits         1       1       0       Six valid bits         1       1       1       Seven valid bits                            |  |  |  |  |  |

|       |                                 | These bits are presented simultaneously with the last bits of data and are cleared by reading the RDSR or by resetting RXENA (bit 4 of RXCSR).                                                                                                                                                                                                                     |  |  |  |  |  |

| 11    | Receiver Overrun<br>(RCV OVRUN) | This bit is used to indicate that an overrun situation has occurred. Overrun exists when the data buffer (bits 0-7 of RDSR) has not been serviced within one character time.                                                                                                                                                                                       |  |  |  |  |  |

|       |                                 | As a general rule, the overrun is indicated when the last bit of the current character has been received into the shift register of the USYNRT and the data buffer is not yet available for a new character.                                                                                                                                                       |  |  |  |  |  |

|       |                                 | Two factors exist which modify this general rule and apply only to bit-oriented protocols.                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|       |                                 | The first factor is the number of bits inserted into the data stream for transparency. For each bit inserted during the formatting of the current character, the controller's maximum response time is increased by one clock cycle.                                                                                                                               |  |  |  |  |  |

|       |                                 | The second factor is the result of termination of the current message. When this occurs, the data of the terminated message which is within the USYNRT is not overrunable. If an attempt is made to displace this data by the reception of a subsequent message, the data of the subsequent message is lost until the data of the prior message has been released. |  |  |  |  |  |

Table 3-3 Receive Data and Status Register (RDSR) Bit Assignments (Cont)

| Bit | Name                                   | Description                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|-----|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 10  | Receiver Abort or<br>Go Ahead (RABORT) | This bit is used only with bit-oriented protocols and indicates that either an abort character or a go-ahead character has been received. This is determined by the Loop Mode bit (PCSAR bit 13). If the Loop Mode bit is clear, RABORT indicates reception of an abort character. If the Loop Mode bit is set, RABORT indicates a go-ahead character has been received.                         |  |  |

|     |                                        | The setting of RABORT causes Receiver Status Ready (bit 10 of RXCSR) to be set.                                                                                                                                                                                                                                                                                                                  |  |  |

|     |                                        | RABORT is reset when the RDSR is read or when Receiver Enable (bit 4 of RXCSR) is reset.                                                                                                                                                                                                                                                                                                         |  |  |

|     |                                        | The abort character is defined to be seven or more contiguous one bits appearing in the data stream. Reception of this bit pattern when Loop Mode is clear causes the receive section of the USYNRT to stop receiving and set RSTARY (bit 10 of RXCSR). The abort character indicates abnormal termination of the current message.                                                               |  |  |

|     |                                        | The go-ahead character is defined as a zero bit followed by seven consecutive one bits. This character is recognized as a normal terminating control character when the Loop Mode bit is set. If Loop Mode is cleared this character is interpreted as an abort character.                                                                                                                       |  |  |

| 9   | Receiver End of<br>Message (REOM)      | This bit is used only with bit-oriented protocols and is asserted if Receiver Active (bit 11 of RXCSR) is set and a message is terminated either normally or abnormally. When REOM becomes set, it sets RSTARY (bit 10 of RXCSR).                                                                                                                                                                |  |  |

|     |                                        | REOM is cleared when RDSR is read or when Receive Enable (bit 4 of RXCSR) is reset.                                                                                                                                                                                                                                                                                                              |  |  |

| 8   | Receiver Start of<br>Message (RSOM)    | Used only with bit-oriented protocols. This bit is presented to the processor along with the first data character of a message and is synchronized to the last received flag character. Setting of RSOM does not set RSTARY (RXCSR bit 10).                                                                                                                                                      |  |  |

|     |                                        | RSOM is cleared by Device Reset, Bus INIT, resetting Receiver Enable (RXCSR bit 4), or the next transfer into the Receive Data buffer (low byte of RDSR).                                                                                                                                                                                                                                        |  |  |

| 7–0 | Receive Data<br>Buffer                 | The low byte of the RDSR is the Receive Data buffer. The serial data input to the USYNRT is assembled and transferred to the low byte of the RDSR for presentation to the processor. When the RDSR receives data, Receive Data Ready (bit 7 of RXCSR) becomes set to indicate that the RDSR has data to be picked up. If this data is not read within one character time, a data overrun occurs. |  |  |

|     |                                        | The characters in the Receive Data buffer are right-justified with bit 0 being the least significant bit.                                                                                                                                                                                                                                                                                        |  |  |

Figure 3-4 Parameter Control Sync/Address Register (PCSAR) Format

Table 3-4 Parameter Control Sync/Address Register (PCSAR) Bit Assignments

| Bit | Name                                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|-----|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 15  | All Parties<br>Addressed (APA)             | This bit is set when automatic recognition of the All Parties Addressed character is desired. The All Parties Addressed character is eight bits of ones with necessary bit stuffing so as not to be confused with the abort character.                                                                                                                                                                                      |  |  |